半导体WAT测试的常见结构

以下文章来源于半导体小马,作者小马

WAT(Wafer Acceptance Test)测试,也叫PCM(Process Control Monitoring),对Wafer划片槽(Scribe Line)测试键(Test Key)的测试,通过电性参数来监控各步工艺是否正常和稳定。

划片槽(Scribe Line)和测试键(Test Key):这是在半导体制造过程中用于WAT测试的两个关键元素。划片槽是沿着晶圆边缘的窄条,用于后续的切割(dicing)过程。测试键则是设在划片槽内或者边缘的特定区域,用于WAT测试。 电性参数:这些参数包括电容、电阻、接触以及金属线路等,这些都是在制造过程中需要监控的重要指标。它们反映了半导体器件的电气特性,如电流传导能力、电压承受能力等。

CP(Circuit Probing)也叫“Wafer Probe”或者“Die Sort”,是对整片Wafer的每个Die的基本器件参数进行测试,例如Vt(阈值电压),Rdson(导通电阻),BVdss(源漏击穿电压),Igss(栅源漏电流),Idss(漏源漏电流)等,把坏的Die挑出来,会用墨点(Ink)标记,可以减少封装和测试的成本,CP pass才会封装,一般测试机台的电压和功率不高,CP是对Wafer的Die进行测试,检查Fab厂制造的工艺水平,把坏的Die挑出来,可以减少封装和测试的成本。

FT(final test)是对封装好的Chip进行Device应用方面的测试,把坏的chip挑出来,FT pass后还会进行process qual和product qual,FT是对package进行测试,检查封装造厂的工艺水平。

广义上的FT也称为ATE(Automatic Test Equipment),一般情况下,ATE通过后可以出货给客户,但对于要求比较高的公司或产品,FT测试通过之后,还有SLT(System Level Test)测试,也称为Bench Test。SLT测试比ATE测试更严格,一般是功能测试,测试具体模块的功能是否正常。经长期的多工况验证,满足更多生产环境和工程环境的要求。

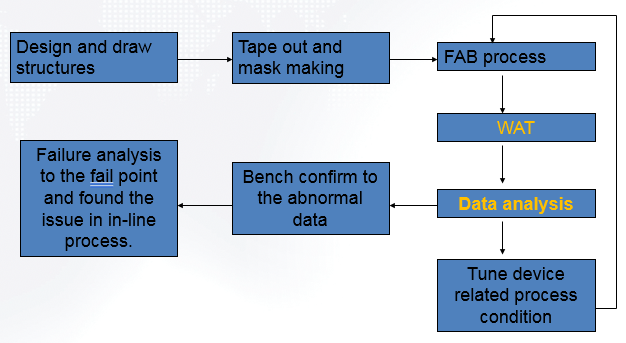

WAT监控工艺一般流程

WAT测试常见结构

隔离结构

隔离结构用于测量黄光、刻蚀与导线相关的能力,如AA,Poly,Metal

测试方法:在两个Pad上加电压测量电流或加电流测量电压

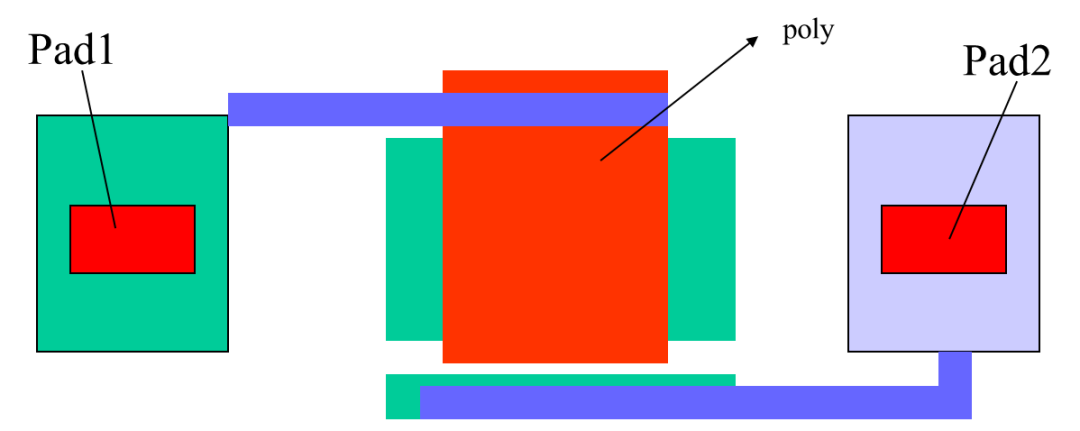

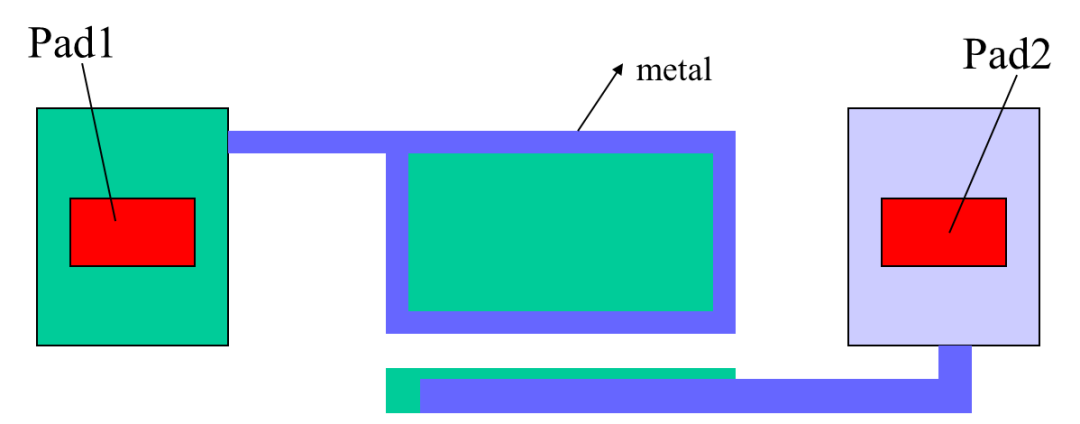

导通结构

导通结构用于测量黄光、刻蚀与导线相关的能力,如AA,Poly,Metal

测试方法:在两个Pad上加电压测量电阻

孔接触结构

孔接触结构用于测量孔相关的工艺能力,如CNT、VIA

测试方法:在两个Pad上加电压测量电阻

薄层电阻结构

薄层电阻结构用于测量导线的Rs,如AA,both silicide and non-silicide, wells, metals

测试方法:在两个Pad上加电压测量电阻

栅介质结构

栅介质结构用于监控栅介质的厚度

测试方法:测量MOS电容的容值,然后计算得出栅介质厚度

接点泄漏结构

用于监控S/D接点漏电流,包括bulk pattern, AA edge pattern, poly finger pattern

测试方法:在两个Pad上加电压测量电流或加电流测量电压

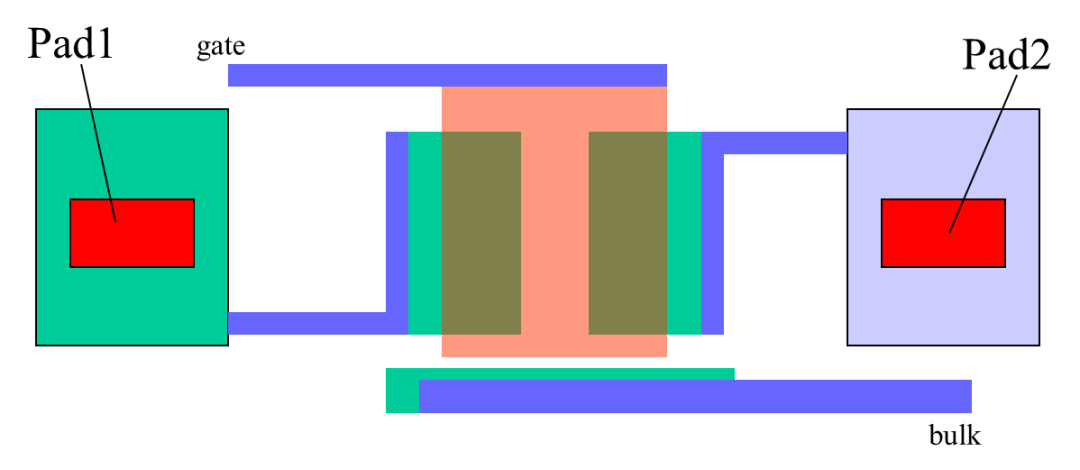

场效应器件结构

用于监控隔离能力,有Poly和Metal 2种结构

测试方法:体硅接地,栅极加载扫描电压,测量Pad间的电流

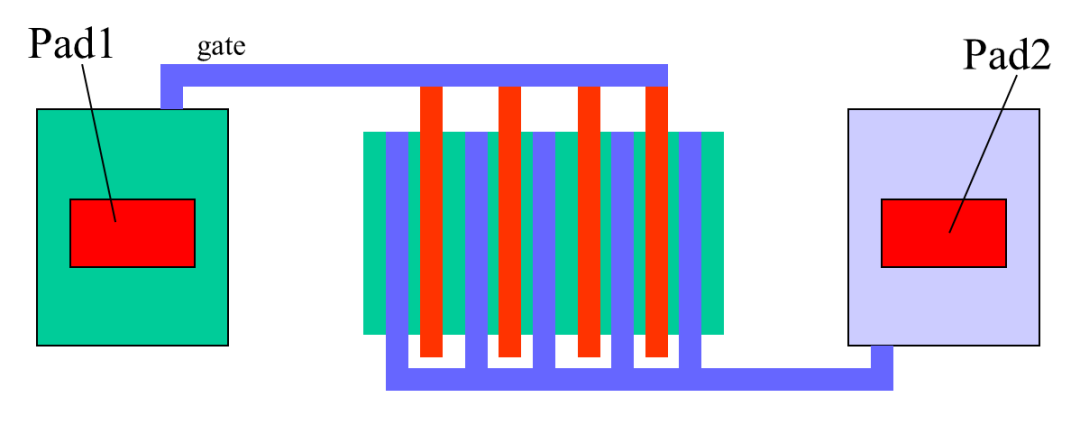

硅化物桥连结构

用于监控Spacer是否存在硅化物残留

测试方法:Pad间加电压,测量电流

器件结构

用于监控器件表现

测试方法:Vt,Ion,Ioff,Idsat,DIBL,Isub,Ig等按定义进行测试,详细说明后续介绍

其它结构

设计规则检查结构,例如结到阱间距规则检查、阱包围规则检查、多晶硅端帽规则检查、接触孔到多晶硅间距规则检查等。

H型器件用于监测器件的 “驼峰现象”(hump phenomena)。

米勒电容用于监测多晶硅的边缘放置误差(E-CD,Edge Critical Dimension)。

使用小电阻监测晶圆允收测试(WAT,Wafer Acceptance Test)探针卡的接触电阻。